虛零點法在模擬CMOS集成電路設計中的應用

模擬CMOS集成電路設計是現代電子系統不可或缺的一部分,尤其在處理連續信號時發揮著關鍵作用。在眾多設計技術中,虛零點法作為一種補償策略,對于提升放大器的穩定性和頻率響應具有顯著效果。本文將探討虛零點法的基本原理及其在模擬CMOS集成電路設計中的實際應用。

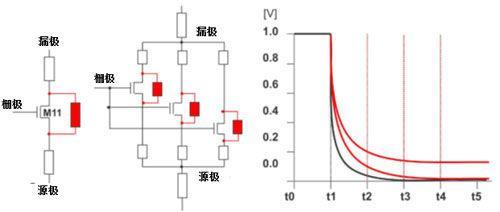

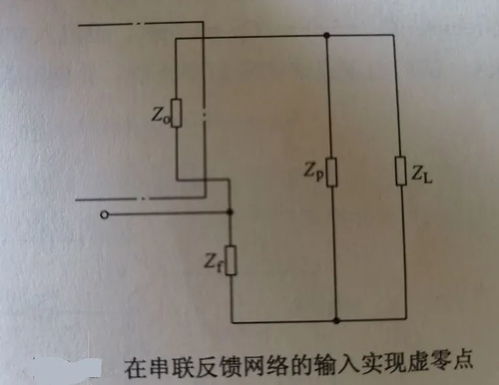

虛零點法是一種通過引入額外的零點來抵消系統極點,從而優化頻率響應的方法。在CMOS放大器中,由于寄生電容和電感的存在,電路常會出現多個極點,導致相位裕度不足和潛在的振蕩問題。虛零點通過在傳輸函數中添加一個位于右半平面的零點(即虛零點),可以有效地補償這些極點,提高系統的穩定性。值得注意的是,虛零點并非真實的物理零點,而是通過電路設計手段模擬出的效果,常用于兩級或多級運算放大器中。

在模擬CMOS集成電路設計中,虛零點法通常通過添加補償電容或電阻網絡來實現。例如,在兩級運算放大器中,第一級的輸出極點可能與第二級的輸入極點相互作用,導致頻率響應下降。通過在補償網絡中引入虛零點,可以調整系統的相位特性,確保在單位增益頻率處有足夠的相位裕度,防止自激振蕩。這種方法簡單且高效,因為它不需要額外的功耗或復雜的電路結構,僅需優化現有元件的參數。

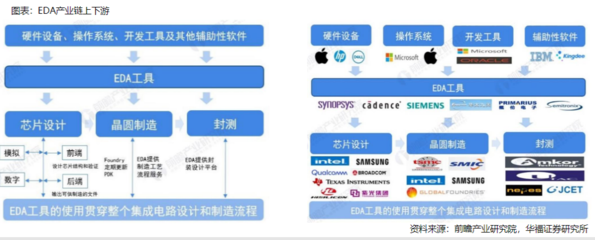

虛零點法的應用不僅限于運算放大器,還擴展至比較器、濾波器和數據轉換器等模塊。在實際設計中,工程師需結合仿真工具(如SPICE)進行精確分析,以確定虛零點的最佳位置。同時,該方法也存在局限性,例如在高頻應用中可能因寄生效應而失效,因此在復雜系統中需與其他補償技術(如米勒補償)結合使用。

虛零點法是模擬CMOS集成電路設計中一種強大的工具,它通過智能補償提升了電路的穩定性和性能。隨著半導體技術的進步,虛零點法將繼續在低功耗、高速應用中發揮重要作用,為電子系統設計提供可靠支持。設計者應深入理解其原理,并結合實際需求靈活應用,以實現更優化的集成電路解決方案。

如若轉載,請注明出處:http://m.mytvb.com.cn/product/8.html

更新時間:2026-01-09 14:59:29