同步時(shí)序原理

同步時(shí)序邏輯是現(xiàn)代數(shù)字集成電路設(shè)計(jì)的核心,它依賴于全局時(shí)鐘信號(hào)來協(xié)調(diào)系統(tǒng)中所有時(shí)序元件的狀態(tài)變化。以下是基于《數(shù)字集成電路:電路與設(shè)計(jì)(第二版)》中關(guān)于同步時(shí)序原理的摘錄與分析。

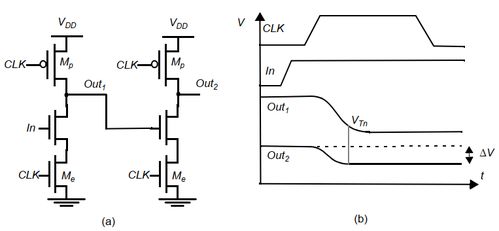

在同步時(shí)序電路中,所有存儲(chǔ)元件(如觸發(fā)器)的狀態(tài)更新都由一個(gè)共同的時(shí)鐘信號(hào)控制。時(shí)鐘信號(hào)通常是周期性的方波,其邊沿(上升沿或下降沿)標(biāo)志著狀態(tài)變化的時(shí)刻。這種設(shè)計(jì)確保了電路的確定性和可靠性,因?yàn)樗胁僮鞫荚陬A(yù)定的時(shí)間間隔內(nèi)發(fā)生,避免了競(jìng)爭(zhēng)條件和毛刺等問題。

同步時(shí)序電路的基本組成包括組合邏輯部分和存儲(chǔ)元件。組合邏輯負(fù)責(zé)根據(jù)當(dāng)前輸入和狀態(tài)生成下一狀態(tài)和輸出,而存儲(chǔ)元件(如D觸發(fā)器)在時(shí)鐘邊沿到來時(shí)鎖存新的狀態(tài)值。關(guān)鍵時(shí)序參數(shù)包括建立時(shí)間(setup time)和保持時(shí)間(hold time),它們定義了輸入信號(hào)在時(shí)鐘邊沿前后必須保持穩(wěn)定的最小時(shí)間窗口,以確保正確操作。

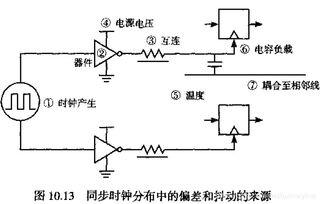

同步設(shè)計(jì)還涉及時(shí)鐘偏移(clock skew)和時(shí)鐘抖動(dòng)(clock jitter)的管理。時(shí)鐘偏移是指時(shí)鐘信號(hào)到達(dá)不同時(shí)序元件的時(shí)間差異,而抖動(dòng)是時(shí)鐘周期的隨機(jī)變化。這些因素會(huì)影響電路的最大工作頻率,必須通過仔細(xì)的布局和時(shí)鐘樹設(shè)計(jì)來最小化。

同步時(shí)序原理通過全局時(shí)鐘同步,為數(shù)字集成電路提供了可預(yù)測(cè)的行為,是高性能、高可靠性系統(tǒng)的基礎(chǔ)。設(shè)計(jì)時(shí)必須嚴(yán)格遵循時(shí)序約束,以避免亞穩(wěn)態(tài)和功能錯(cuò)誤。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.mytvb.com.cn/product/4.html

更新時(shí)間:2026-01-09 22:11:44