數字集成電路設計流程詳解

數字集成電路設計是一項復雜且系統性的工程,涵蓋從概念到芯片實現的多個階段。其典型設計流程主要包括以下幾個關鍵步驟:

- 規格定義:首先明確芯片的功能、性能指標、功耗要求、工作電壓及接口規范等。這一階段需與客戶或系統工程師充分溝通,確保設計目標清晰可行。

- 架構設計:基于規格,設計整體系統架構,包括模塊劃分、數據流控制、時鐘域分配等。通常使用高級建模語言(如SystemC或MATLAB)進行行為級仿真驗證。

- RTL設計:采用硬件描述語言(如Verilog或VHDL)編寫寄存器傳輸級代碼,描述數字電路的功能邏輯。此階段需確保代碼風格規范,便于后續綜合與驗證。

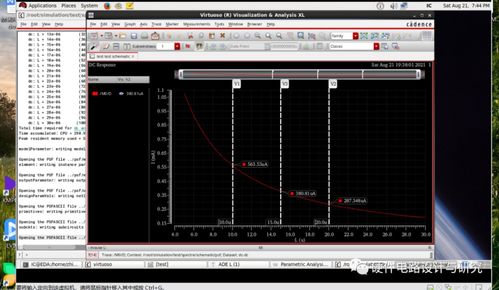

- 功能驗證:通過仿真工具(如VCS、ModelSim)對RTL代碼進行測試,檢查其是否符合規格要求。常用方法包括定向測試、隨機測試和斷言驗證,以覆蓋各種邊界情況。

- 邏輯綜合:使用綜合工具(如Design Compiler)將RTL代碼轉換為門級網表,同時進行時序優化和面積約束。此步驟需指定目標工藝庫,并生成時序報告供分析。

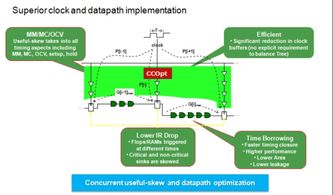

- 物理設計:將門級網表轉換為實際布局,主要包括布局規劃、單元放置、時鐘樹綜合、布線等。物理設計需考慮信號完整性、電源規劃和制造工藝限制。

- 時序與功耗分析:使用靜態時序分析工具(如PrimeTime)檢查建立時間和保持時間是否滿足要求,并通過功耗分析工具評估動態與靜態功耗,必要時進行優化。

- 設計規則檢查與版圖驗證:對最終版圖進行DRC(設計規則檢查)和LVS(版圖與原理圖對比),確保符合代工廠的制造規范。

- 流片與測試:完成所有驗證后,將版圖數據提交給晶圓廠進行制造。芯片返回后,通過測試設備對樣品進行功能、性能和可靠性測試。

整個設計流程通常采用迭代方式,任一階段發現問題均需返回前期步驟修改。隨著工藝節點進步,設計復雜度日益增加,團隊需借助EDA工具和IP復用技術以提高效率。低功耗設計、可測性設計和安全考量已成為現代數字IC設計不可或缺的環節。

如若轉載,請注明出處:http://m.mytvb.com.cn/product/3.html

更新時間:2026-01-09 23:44:35